# Intel® Atom<sup>™</sup> Processor S1200 Product Family for Microserver

Datasheet, Volume 1 of 2

December 2012

Document Number: 328194-001

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/#/en\_US\_01

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Go to: http://www.intel.com/products/processor%5Fnumber/

Code Names are only for use by Intel to identify products, platforms, programs, services, etc. ("products") in development by Intel that have not been made commercially available to the public, i.e., announced, launched or shipped. They are never to be used as "commercial" names for products. Also, they are not intended to function as trademarks.

BiueMoon, BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino Inside, Cilk, Core Inside, E-GOLD, 1960, Intel, the Intel logo, Intel AppUp, Intel Atom, Intel Atom Inside, Intel Core, Intel Inside, Intel Insider, the Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel Sponsors of Tomorrow., the Intel Sponsors of Tomorrow. logo, Intel StrataFlash, Intel VPro, Intel XScale, InTru, the InTru logo, the InTru Inside logo, InTru soundmark, Itanium, Itanium Inside, MCS, MMX, Moblin, Pentium, Pentium Inside, Puma, skoool, the skoool logo, SMARTI, Sound Mark, The Creators Project, The Journey Inside, Thunderbolt, vPro Inside, VTune, Xeon, Xeon Inside, X-GOLD, XMM and XPOSYS are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2012, Intel Corporation. All rights reserved.

2

## **Revision History**

| Date          | Revision | Description      |

|---------------|----------|------------------|

| November 2012 | 1.0      | Initial release. |

## Contents

| 1 | Over | view     |                    |                                                                        | 9    |

|---|------|----------|--------------------|------------------------------------------------------------------------|------|

|   | 1.1  | Introdu  | uction             |                                                                        | 9    |

|   | 1.2  | Key Fea  | atures of t        | the Processor                                                          | .11  |

|   |      | 1.2.1    | Intel® A           | tom™ Core Features and Caching Hierarchy                               | .13  |

|   |      |          | 1.2.1.1            |                                                                        |      |

|   |      | 1.2.2    | UnCore F           | eatures                                                                |      |

|   |      |          | 1.2.2.1            | Integrated Memory Controller (iMC)                                     |      |

|   |      |          | 1.2.2.2            | Integrated I/O (IIO)                                                   |      |

|   |      | 1.2.3    | Legacy L           | /O Features                                                            |      |

|   | 1.3  | Power    |                    | ent Support                                                            |      |

|   |      | 1.3.1    |                    | anagement Features                                                     |      |

|   | 1.4  | Therma   |                    | ment Support                                                           |      |

|   | 1.5  |          |                    | ry                                                                     |      |

|   | 1.6  | -        |                    | · · · · · · · · · · · · · · · · · · ·                                  |      |

|   | 1.7  |          | 05                 | nts                                                                    |      |

|   | 1.8  |          |                    |                                                                        |      |

| • |      |          |                    |                                                                        |      |

| 2 |      |          |                    | • · · ·                                                                |      |

|   | 2.1  | 0        |                    | bry Controller                                                         |      |

|   |      | 2.1.1    |                    | tion                                                                   |      |

|   |      | 2.1.2    |                    | d Features                                                             |      |

|   |      | 2.1.3    |                    | al Description                                                         |      |

|   |      |          | 2.1.3.1            | DRAM Requests and Data Ordering                                        |      |

|   |      |          | 2.1.3.2            | DRAM Out of Bound Access                                               |      |

|   | 2.2  |          | 2.1.3.3            | DRAM Power Management                                                  |      |

|   | 2.2  |          |                    | rface                                                                  |      |

|   |      | 2.2.1    |                    | ess Root Port Features and Functions                                   |      |

|   |      | 2.2.2    | •                  | ess Architecture                                                       |      |

|   |      |          | 2.2.2.1            | Transaction Layer                                                      |      |

|   |      |          | 2.2.2.2            | Data Link Layer                                                        |      |

|   |      | <b>.</b> | 2.2.2.3            | Physical Layer                                                         |      |

|   | 2.3  | 2.2.3    |                    | ess Configuration Mechanism                                            |      |

|   | 2.3  |          |                    |                                                                        |      |

|   | 2.4  | 2.3.1    |                    | Management                                                             |      |

|   | 2.4  | -        |                    | y I/O Overview                                                         |      |

|   |      | 2.4.1    |                    | ed UART (HSUART)                                                       |      |

|   |      | 2.4.2    | Low Pin (          | Count (LPC) Interface                                                  | .33  |

|   |      | 2.4.3    |                    | CPU Interface Signals                                                  |      |

|   |      |          | 2.4.3.1            | CPU Interface Signal - INIT#                                           |      |

|   |      |          | 2.4.3.2            | CPU Interface Signal - NMI                                             |      |

|   |      |          | 2.4.3.3            | CPU Interface Signal - INTR<br>CPU Interface Signal - SMI#             | . 33 |

|   |      | 2.4.4    |                    |                                                                        |      |

|   |      |          |                    | nced Programmable Interrupt Controller (IOxAPIC)<br>Purpose I/O (GPIO) |      |

|   |      | 2.4.5    |                    |                                                                        |      |

|   |      | 2.4.6    |                    | ripheral Interface (SPI)                                               |      |

|   |      | 2.4.7    |                    | e Clock                                                                |      |

|   |      | 2.4.8    |                    | grammable Interval Timer (PIT)                                         |      |

|   |      |          | 2.4.8.1            | Counter 0, System Timer                                                | .36  |

|   |      |          | 2.4.8.2            | Counter 1, Refresh-Cycle Toggle Status                                 |      |

|   |      |          | 2.4.8.3<br>2.4.8.4 | Counter 2, Speaker Tone                                                |      |

|   |      | 240      |                    | Timer I/O Registers<br>errupt Controllers (PIC)                        |      |

|   |      | 2.4.9    |                    |                                                                        |      |

|   |      |          | 2.4.9.1            | I/O Registers                                                          | . 39 |

|   |      | 2.4.10 High-Precision Event Timer (HPET)               |

|---|------|--------------------------------------------------------|

|   |      | 2.4.10.1 HPET MMIO Registers                           |

|   |      | 2.4.11 SMBus 1.0 Controller                            |

|   |      | 2.4.12 System Audio Speaker                            |

|   |      | 2.4.13 Watchdog Timer (WDT)                            |

|   |      |                                                        |

| 3 | Tech | 1 <b>ologies</b>                                       |

|   | 3.1  | Intel® Virtualization Technology (Intel® VT)           |

|   |      | 3.1.1 Intel VT-x Objectives 43                         |

|   |      | 3.1.2 Intel VT-x Features 44                           |

|   | 3.2  | Security Technologies 45                               |

|   |      | 3.2.1 Execute Disable Bit                              |

|   | 3.3  | Intel® Hyper-Threading Technology 45                   |

|   | 3.4  | Enhanced Intel SpeedStep® Technology 45                |

| 4 | Powe | r Management                                           |

| - | 4.1  | Overview                                               |

|   | 7.1  | 4.1.1 Acronyms                                         |

|   |      | 4.1.2 Power Management Features                        |

|   | 4.2  | Communication with the External Circuitry              |

|   | 4.3  | Power Planes and Voltage Rails                         |

|   | 4.5  | 4.3.1 Power Group Definitions                          |

|   |      | 4.3.1 Fower Group Deminions                            |

|   |      | 4.3.1.2 SUS Power Well                                 |

|   |      | 4.3.1.2 S03 Power Well                                 |

|   |      | 4.3.2 Power Plane vs. Supported System Sleep States    |

|   |      | 4.3.3 Voltage Sequencing Requirements                  |

|   |      | 4.3.4 Voltage Rail Ramp Rate                           |

|   |      | 4.3.5 SerialVID (SVID) Overview                        |

|   | 4.4  | ACPI State Descriptions                                |

|   | 4.5  | Performance States (P-States) and Throttling           |

|   | 4.5  | 4.5.1 Enhanced Intel SpeedStep <sup>®</sup> Technology |

|   |      | 4.5.2 Dynamic Power Management on I/O                  |

|   |      | 4.5.2.1 LPC Clock Control                              |

|   | 4.6  | Processor Core States (C-State)                        |

|   | 4.0  | 4.6.1 C-State Variations                               |

|   |      | 4.6.2 C-State Definition                               |

|   |      | 4.6.2.1 C0 State – Full On                             |

|   |      | 4.6.2.2 C1 State – Auto-Halt                           |

|   |      | 4.6.2.3 C2 State – Stop Grant                          |

|   |      | 4.6.2.4 C4 State – Deeper Sleep                        |

|   |      | 4.6.2.5 C6 - Deep Power Down Technology                |

|   |      | 4.6.2.6 C6 Demotion Policy                             |

|   |      | 4.6.3 Extended Low Power States                        |

|   |      | 4.6.4 C2 Popup/Popdown                                 |

|   |      | 4.6.5 Recommended C-State Configurations               |

|   |      | 4.6.6 Hardware Coordination of C-States                |

|   |      | 4.6.7 I/O Based C-State Hardware Coordination          |

|   |      | 4.6.8 C-States from I/O Instruction Decoded to MWAIT   |

|   |      | 4.6.9 C1 BIOS Coordination                             |

|   |      | 4.6.10 CPU C-State Triggering                          |

|   | 4.7  | Transition Rules Among C States and S States           |

|   | 4.8  | System Sleep State Control (S States)                  |

|   |      | 4.8.1 S-State Definition                               |

|   |      | 4.8.1.1 S0 - Full On                                   |

|   |      |                                                        |

|   |              |          | 4.8.1.2            | S3 - Suspend to RAM (Standby)                                                       | 70          |

|---|--------------|----------|--------------------|-------------------------------------------------------------------------------------|-------------|

|   |              |          | 4.8.1.3            | S4 - Suspend to Disk (Hibernate)                                                    |             |

|   |              | 100      | 4.8.1.4            | S5 - Soft Off                                                                       |             |

|   |              | 4.8.2    |                    | ell Transition Sequence                                                             |             |

|   |              |          | 4.8.2.1<br>4.8.2.2 | RTC Power Well Transition (G5 -> G3)<br>Transition without G3/G2                    |             |

|   |              |          | 4.8.2.3            | SUS Power Well Transition                                                           |             |

|   |              | 4.8.3    |                    | ate Transitions                                                                     |             |

|   |              |          | 4.8.3.1            | Initiating Sleep States                                                             |             |

|   |              |          | 4.8.3.2            | S3-to-SO Sleep Exit Sequence and Timing                                             |             |

|   |              |          | 4.8.3.3            | S4/5-S0 Sleep Exit Sequence and Timing                                              |             |

|   | 4.9          | Main M   |                    | wer Management                                                                      |             |

|   |              | 4.9.1    |                    | ower-Up                                                                             |             |

|   |              | 4.9.2    |                    | ystem Operation                                                                     |             |

|   |              |          |                    | DDR3 Power-Down Modes                                                               |             |

|   |              |          | 4.9.2.2            | DDR3 Self-Refresh Mode                                                              |             |

| 5 | Ther         |          |                    | <b>t</b>                                                                            |             |

|   | 5.1          | Intel®   | Thermal N          | 1onitor                                                                             | 80          |

|   | 5.2          |          |                    | lonitor 2                                                                           |             |

|   | 5.3          |          |                    | gnal Pin                                                                            |             |

|   | 5.4          |          |                    | e                                                                                   |             |

|   | 5.5          |          |                    |                                                                                     |             |

|   | 5.6          |          |                    | ermal Sensor (DTS)                                                                  |             |

|   | 5.7          |          |                    | isor                                                                                |             |

|   | 5.8<br>5.9   |          |                    | rheating Thermal Sensor<br>g of DRAM Transactions                                   |             |

|   | 5.10         |          |                    |                                                                                     |             |

|   | 5.11         |          |                    | and Status Registers                                                                |             |

|   | 5.11         |          |                    | Diode Offset Register                                                               |             |

|   |              |          |                    | nce Status Register                                                                 |             |

|   |              |          |                    | ric (RTF) Thermal Throttle Register                                                 |             |

|   |              |          |                    | el <sup>®</sup> Thermal Monitor Control Register - Clock Modulation                 |             |

|   |              | 5.11.5   | ACPI Inte          | el <sup>®</sup> Thermal Monitor Interrupt Control Register - Thermal                | Interrupt86 |

|   |              | 5.11.6   | ACPI Inte          | el <sup>®</sup> Thermal Monitor Status Register - Thermal Sensor                    |             |

|   |              | 5.11.7   | ACPI Inte          | ا ${}^{\mathbb{R}}_{\mathbb{Q}}$ Thermal Monitor Control Register - Thermal Control | 86          |

|   |              | 5.11.8   | ACPI Inte          | $\mathfrak{el}^{\mathbb{R}}$ Thermal Monitor Control Register - Thermal Status      | 86          |

| 6 | Signa        | al Descr | iptions            |                                                                                     |             |

| - | 6.1          |          |                    | emory Signals                                                                       |             |

|   | 6.2          |          |                    | Port Signals                                                                        |             |

|   | 6.3          |          |                    | PC) Signals                                                                         |             |

|   | 6.4          |          |                    | ls                                                                                  |             |

|   | 6.5          |          |                    | mory Signals                                                                        |             |

|   | 6.6          |          |                    | ower Management Signals                                                             |             |

|   | 6.7          |          |                    | Signals                                                                             |             |

|   | 6.8          |          |                    | ment Signals                                                                        |             |

|   | 6.9          |          |                    | ۲ Signals                                                                           |             |

|   | 6.10         |          |                    | I/O Signals                                                                         |             |

|   | 6.11         |          |                    | nd HPET Signals                                                                     |             |

|   | 6.12         |          |                    | and Error Signals                                                                   |             |

|   | 6.13<br>6.14 |          |                    | ition Control Signals<br>d Signals                                                  |             |

|   |              |          |                    | 0                                                                                   |             |

| 7 | Elect        | -        |                    | ns                                                                                  |             |

|   | 7.1          |          |                    | al Voltage Requirements                                                             |             |

|   | 7.2          | DC Pow   | ver Charad         | teristics                                                                           |             |

7.3Signal Input and Output Operational DC Characteristics1128Component Ball-Out Listing1158.1Sorted by Signal Name1158.2Sorted by Ball Number1348.3Ball Map1529Package Mechanical Characteristics161

## **Figures**

| 1-1 | Multi-Node Microserver Configuration                                                        | 9   |

|-----|---------------------------------------------------------------------------------------------|-----|

| 1-2 | SMB Server Configuration                                                                    |     |

| 1-3 | Intel® Atom <sup>™</sup> Processor S1200 Product Family for Microserver High-Level Block Di |     |

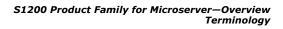

| 2-1 | PCI Express Layering Diagram                                                                |     |

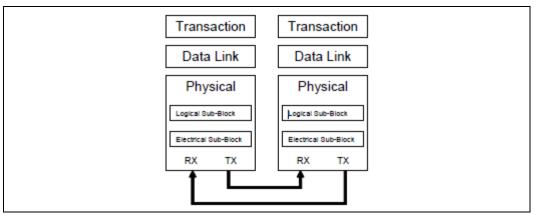

| 2-2 | Packet Flow through the Layers                                                              |     |

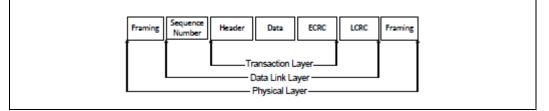

| 4-1 | Power Management System Connectivity                                                        |     |

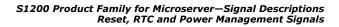

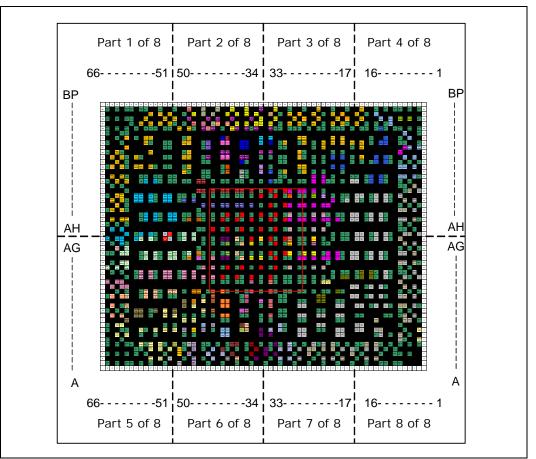

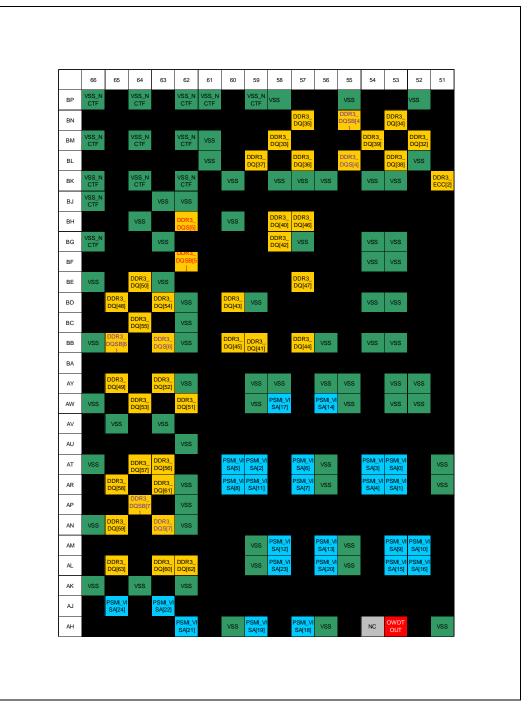

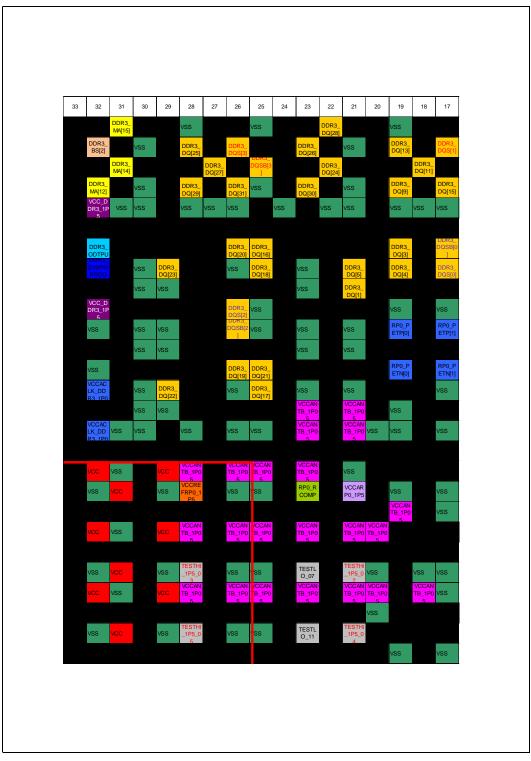

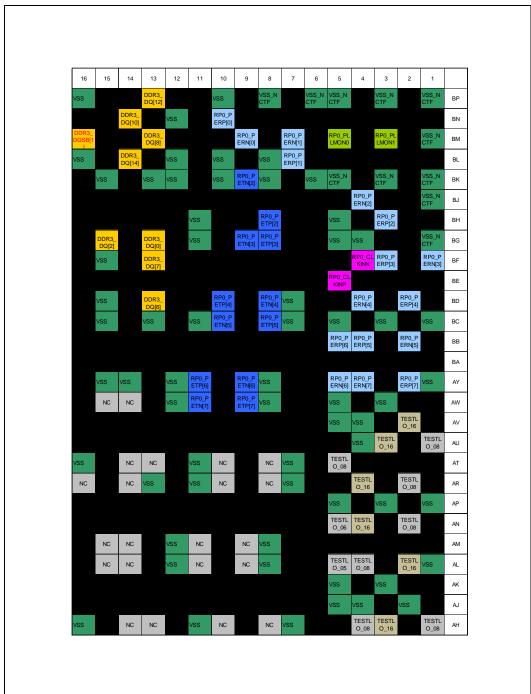

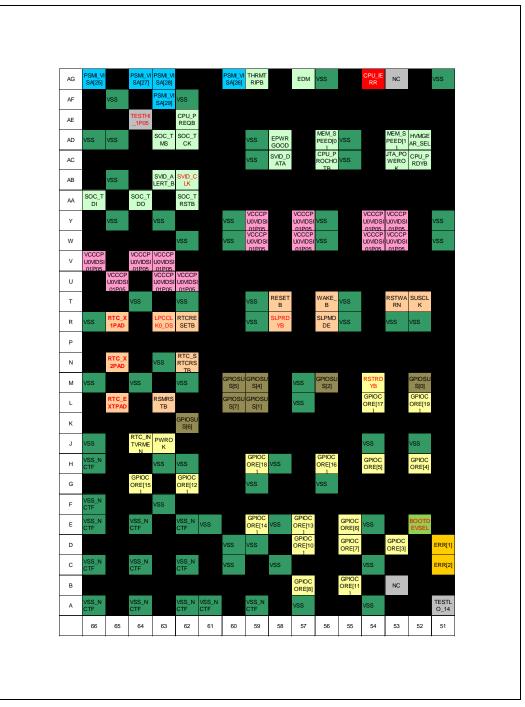

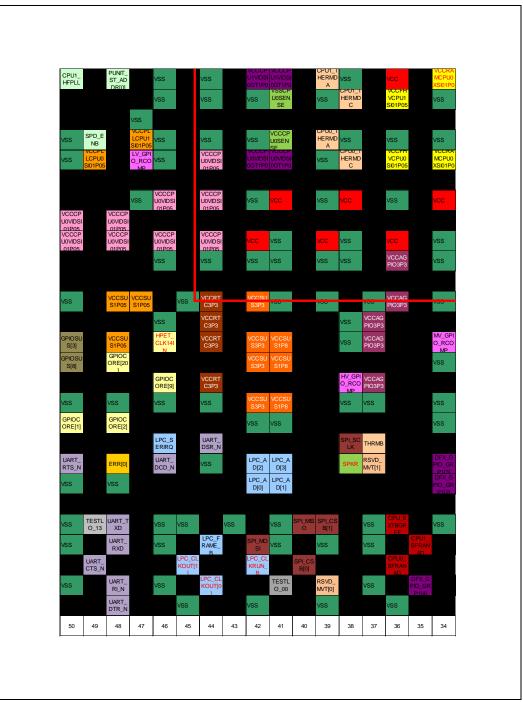

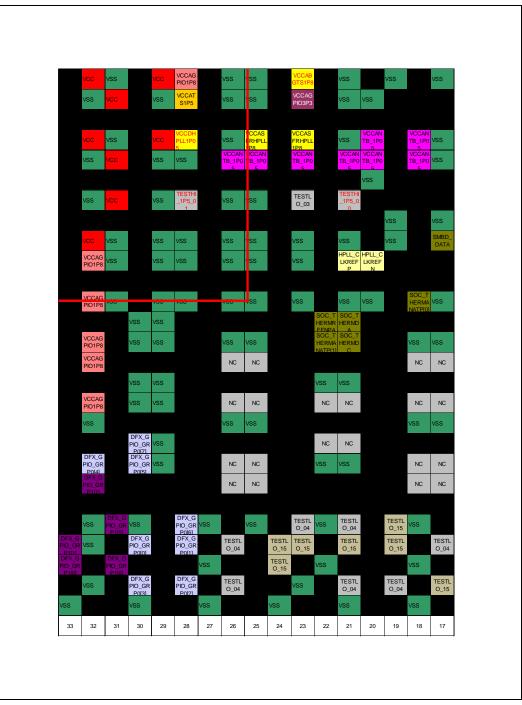

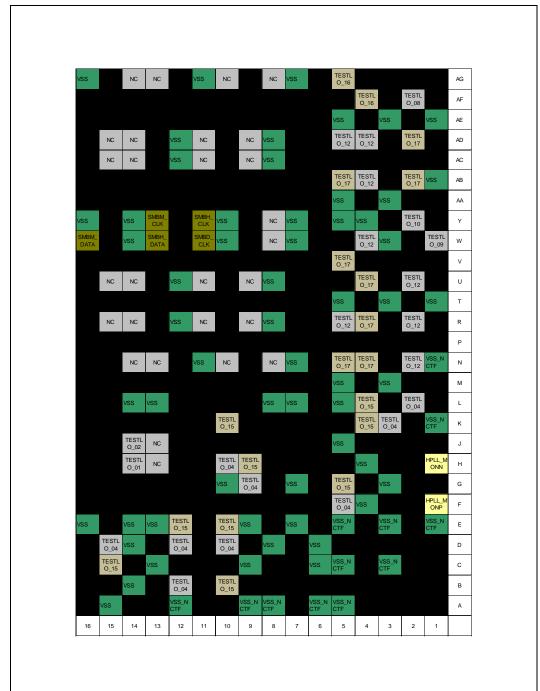

| 8-1 | Ball Map                                                                                    | 152 |

| 8-2 | Ball Map - Part 1 of 8                                                                      | 153 |

| 8-3 | Ball Map - Part 2 of 8                                                                      |     |

| 8-4 | Ball Map - Part 3 of 8                                                                      | 155 |

| 8-5 | Ball Map - Part 4 of 8                                                                      | 156 |

| 8-6 | Ball Map - Part 5 of 8                                                                      |     |

| 8-7 | Ball Map - Part 6 of 8                                                                      |     |

| 8-8 | Ball Map - Part 7 of 8                                                                      |     |

| 8-9 | Ball Map - Part 8 of 8                                                                      |     |

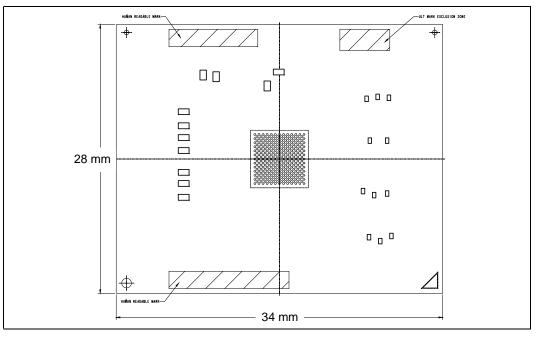

| 9-1 | Topside Showing Capacitors and Marking Areas                                                |     |

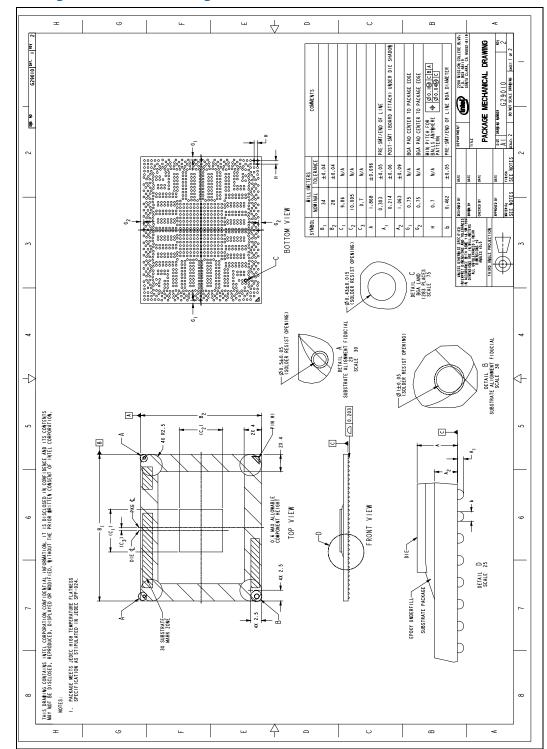

| 9-2 | Package Mechanical Drawing                                                                  |     |

## **Tables**

| 1    | Intel® Atom <sup>™</sup> Processor S1200 Product Family                                | . 9 |

|------|----------------------------------------------------------------------------------------|-----|

| 1-2  | Technologies in Processor Core                                                         | 13  |

| 1-3  | Processor Terminology                                                                  | 19  |

| 1-4  | Related Documents                                                                      | 21  |

| 2-1  | PCI Configuration Registers for LPC Bridge - Bus 0, Device 31, Function 0              | 31  |

| 2-2  | Timer I/O Registers                                                                    |     |

| 2-3  | Interrupt Controller Core Connections                                                  |     |

| 2-4  | Register Table                                                                         |     |

| 2-5  | HPET MMIO Registers                                                                    |     |

| 4-1  | Power Management Acronyms                                                              |     |

| 4-2  | Power Management Signal Pins                                                           |     |

| 4-3  | Power Planes and Supported System Sleep States                                         |     |

| 4-4  | Dynamic VID Slew Rate                                                                  |     |

| 4-5  | General Power States for Systems Using the Intel® Atom™ Processor S1200 Product Family |     |

| 4-6  | ACPI Power Management State Transitions                                                |     |

| 4-7  | Processor C States                                                                     |     |

| 4-8  | Thread Coordination Logic for C-States (Per Core)                                      |     |

| 4-9  | FTH MWAIT Parameters                                                                   |     |

| 6-1  | Buffer Types                                                                           |     |

| 6-2  | System Memory Signals                                                                  |     |

| 6-3  | PCI Express Root Port Unit 0 Signals                                                   |     |

| 6-4  | LPC Interface Signals                                                                  |     |

| 6-5  | SMBus Interface Signals                                                                |     |

| 6-6  | SPI Interface Signals                                                                  |     |

| 6-7  | Reset, RTC and Power Management Interface Signals                                      |     |

| 6-8  | JTAG and Debug Interface Signals                                                       |     |

| 6-9  | Thermal Management Signals                                                             |     |

| 6-10 | High-Speed UART Signals                                                                |     |

| 6-11 | General-Purpose I/O Signals                                                            |     |

|      | Speaker, WDT and HPET Signals                                                          |     |

|      | Processor Clock and Error Signals                                                      |     |

| 6-14 | Buffer Compensation Control Signals                                                    |     |

| 6-15 | Power and Ground Signals                                                               |     |

| 7-1  | Voltage Source Operational Requirements                                                |     |

| 7-2  | Power Well Information                                                                 |     |

| 7-3  | Intel <sup>®</sup> Atom™ Processor S1240 SKU (1.5V DDR3):                              | 00  |

|      | Voltage Source DC Characteristics (TDP@Tj=102C and MAX@Tj=102C)                        | 06  |

| 7-4  | Intel <sup>®</sup> Atom <sup>™</sup> Processor S1240 SKU (1.35V DDR3-L):               |     |

|      | Voltage Source DC Characteristics (TDP@Tj=102C and MAX@Tj=102C)1                       | 07  |

| 7-5  | Intel <sup>®</sup> Atom <sup>™</sup> Processor S1220 SKU (1.5V DDR3):                  |     |

|      | Voltage Source DC Characteristics (TDP@Tj=95C and MAX@Tj=95C)1                         | 80  |

| 7-6  | Intel <sup>®</sup> Atom <sup>™</sup> Processor S1220 SKU (1.35V DDR3-L):               |     |

|      | Voltage Source DC Characteristics (TDP@Tj=95C and MAX@Tj=95C)1                         | 09  |

| 7-7  | Intel <sup>®</sup> Atom <sup>™</sup> Processor S1260 SKU (1.5V DDR3)                   |     |

|      | Voltage Source DC Characteristics (TDP@Tj=95C and MAX@Tj=95C)1                         | 10  |

| 7-8  | Intel <sup>®</sup> Atom <sup>™</sup> Processor S1260 SKU (1.35V DDR3-L)                |     |

| 7 6  | Voltage Source DC Characteristics (TDP@Tj=95C and MAX@Tj=95C)                          |     |

| 7-9  | Signal DC Operational Characteristics                                                  |     |

| 8-1  | Ball-out Sorted by Signal Name                                                         |     |

| 8-1  | Ball-out Sorted by Signal Name                                                         |     |

| 8-2  | Ball-out Sorted by Ball Number1                                                        | 35  |

§§

I

## **1** Overview

## **1.1** Introduction

The Intel® Atom<sup>™</sup> Processor S1200 Product Family for Microserver is the new generation of SoC 64-bit processors built using Intel 32-nanometer process technology. Throughout this document, the Intel® Atom<sup>™</sup> Processor S1200 Product Family for Microserver is also referred to as the processor, SoC, or S12x0.

This document relates to the following product SKUs:

#### Table 1. Intel® Atom™ Processor S1200 Product Family

| SKU Name                                 | TDP  |

|------------------------------------------|------|

| Intel <sup>®</sup> Atom™ Processor S1260 | 8.5W |

| Intel <sup>®</sup> Atom™ Processor S1240 | 6.3W |

| Intel <sup>®</sup> Atom™ Processor S1220 | 8.1W |

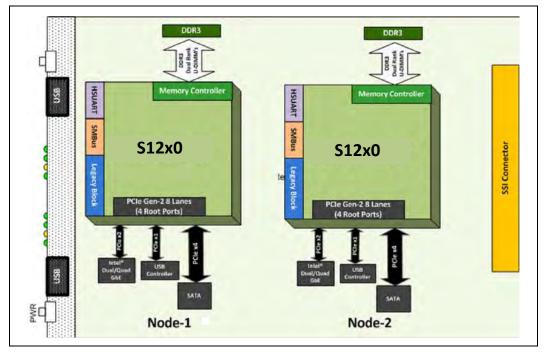

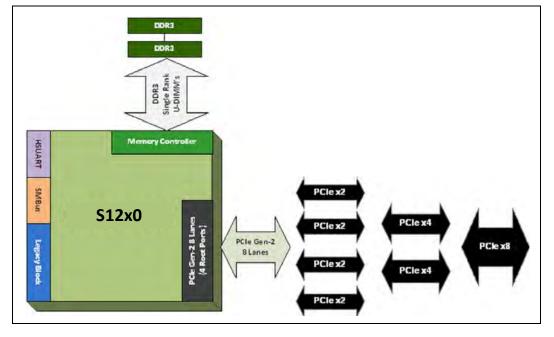

The SoC is targeted for segments focusing on highly dense, low power server configurations (i.e., Microserver) as shown in Figure 1-1 and the traditional Small and Medium Business (SMB) server segment as shown in Figure 1-2.

#### Figure 1-1. Multi-Node Microserver Configuration

#### Figure 1-2. SMB Server Configuration

## **1.2 Key Features of the Processor**

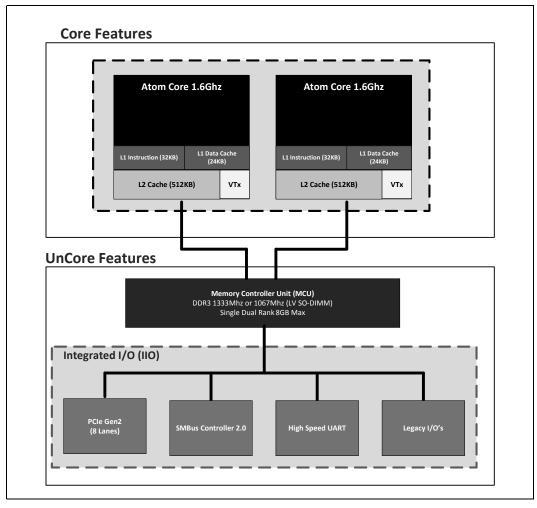

- Number of cores: Dual core with two threads per core

- Operating Frequency: 1.6GHz/2.0GHz depending on the SKU

- Cache/Core Includes:

- 32KB, 4-way L1 instruction cache

- 24KB, 6-way L1 data cache

- 512KB, 8-way L2 Cache per Core (Total of 1024KB)

- Supports 36-bit physical addressing

- Target TDP (Thermal Design Power) Consumption:

- 8.5W Intel Atom Processor S1260 SKU

- 6.3W Intel Atom Processor S1240 SKU

- 8.1W Intel Atom Processor S1220 SKU

- Supports C1, C2, C4 and C6 CPU states

- Supports single channel DDR3 with ECC support:

- 72-bits data bus (64bit data + 8 bit ECC)

- 1067MT/s and 1333MT/s data rate with U-DIMM and SO-DIMM support

- Supports single, dual, or two single-rank DIMM

- Supported memory size from 512MB to 8GB with x8/x16 DRAM devices (x16 device with non-ECC only)

- Supported DRAM densities 1Gb, 2Gb and 4Gb device technology

- Low Voltage (LV) SO-DIMM is supported at 1066MT

- Supporting up to 8 lanes with up to four PCIe\* Gen 2 ports (controllers). These can be configured as:

- One PCIe x8 ports OR

- Two PCIe x4 ports OR

- Four PCIe x2 ports OR

- One PCIe x4 and Two PCIe x2ports

- Memory RAS Features Includes:

- Hardware based Memory Scrubbing (Demand and Patrol Scrubs)

- Data and Address Parity Protection (SEC-DED-ECC)

- Error Injection

- Data Scrambling

- Memory Region Isolation

- Supports Intel® 64-bits with CPU virtualization VTx

- Integrated Legacy Interfaces includes:

- SMBus

- GPIO

- High Speed UART

- LPC Bus

This section describes the key S12x0 architecture features of the Core and UnCore modules of the S12x0 family.

T

L

### **1.2.1** Intel® Atom<sup>™</sup> Core Features and Caching Hierarchy

- 1.6GHz/2.0GHz Intel® Atom<sup>™</sup> Core, Two Cores support.

- Features per core:

- Two thread per Core.

- Support for Intel<sup>®</sup> 64 Bits, VT*x* Compatible.

- 36 bits physical address.

- Caching Hierarchy two levels:

- 32KB, 4-way L1 Instruction Cache (ICU).

- 24KB, 6-way L1 Data Cache (DCU).

- 512KB, 8-way L2 cache.

- Addressing Space:

- 36 bits physical address.

- 48 bits virtual address space.

#### **1.2.1.1 Processor Core Technologies**

The S12x0 core offers several technologies. Table 1-2 describes these technologies implemented by the S12x0 core.

#### Table 1-2. Technologies in Processor Core

| Name                                                     | Short Description                                                                                                                                                                        |  |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VTx                                                      | VT eXtension supports virtualization of processor hardware for a multiple software environment.                                                                                          |  |

| Execute Disable Bit                                      | Execute Disable Bit: The Intel Execute Disable Bit functionality can help prevent certain classes of malicious buffer overflow attacks when combined with a supporting operating system. |  |

| Hyper-Threading Technology                               | Intel® Hyper-Threading Technology: Allows each Intel Atom execution core to function as two logical processors.                                                                          |  |

| Enhanced Intel SpeedStep <sup>®</sup><br>Technology      | Enhanced Intel SpeedStep® Technology: Enables very high performance while meeting the power-conservation needs of the platform.                                                          |  |

| Intel <sup>®</sup> Thermal Monitor and Thermal Monitor 2 | Briarwood core processor supports a digital thermal sensor that will provide per thread temperatures.                                                                                    |  |

| SSE 3.0                                                  | Streaming SIMD Extensions 3.0                                                                                                                                                            |  |

### **1.2.2 UnCore Features**

This section describes key features supported by each of the UnCore modules designed specifically for the microserver processor segment. Detailed descriptions of these key modules is provided in subsequent chapters.

### **1.2.2.1** Integrated Memory Controller (iMC)

The S12x0 contains an integrated 72-bit single channel memory controller that supports discrete DDR3 DRAM devices, a single dual-rank DIMM, or two single-rank DIMMs. The data bus width of 72 bits supports 64-bit data and an 8-bit ECC.

Key features are as follows:

- Single channel DDR3 memory controller:

- One or Two rank UDIMMs and VLP DIMMs support

- DIMMs supports include 1.5V Only

- SO-DIMMs supports include both 1.5V and Low Voltage (LV) 1.35V SO-DIMMs

- Supports 1066 MT/s (*Max speed supported with Low Voltage SO-DIMM*) and 1333MT/s DDR3 frequencies

- Supports total memory size of 512MB up to 8GB:

- Supports x8 and x16 (x16 device with non-ECC only) DRAM device widths

- Supports 1Gb, 2Gb and 4Gb DRAM device densities

- Supports 1 or 2 ranks (2 chip selects), dual ranks must be identical

- 72-bit data bus (64-bit data and 8-bit SEC-DED-ECC):

- · Supported data reliability features

- Demand and Patrol memory scrub

- Error injection on write/read data paths including address matching

- DDR Data Scrambler to reduce power supply noise, improve signal integrity and to encrypt/protect the contents of memory

- · Supports different physical address mappings to optimize for performance

- · Aggressive power management to reduce power consumption

- Supports 1N/2N/3N mode for DRAM command

- Out-of-order request service for increased performance

- · Opportunistic and per-rank refresh for reduced performance impact

#### 1.2.2.2 Integrated I/O (IIO)

The S12x0 provides an integrated I/O module, which consists of high-speed and legacy I/O interfaces.

Features included are:

- PCI Express\* Version 2.1 Root Port interfaces Up to eight lanes of PCIe

- Supports up to eight lanes with up to four PCIe gen2 root ports (controllers).

- System Management bus (SMBus 2.0) Controller

- Legacy I/O

Т

#### **1.2.2.2.1** PCI Express Interface (PCIe)

S12x0 provides a number of integrated PCI Express Gen2 Root Ports for flexible I/O connectivity. The following are key attributes of the PCI Express interface:

- Gen2 speeds at 5GT/s (backward compatible to PCIe Gen1 2.5GT/s)

- x8 interface bifurcated down to one x8 or two x4 or four x2

#### 1.2.2.2.2 System Management Bus (SMBus) 2.0 Controller

The S12x0 provides two System Management Bus (SMBus) 2.0 host controllers.

An SMBus controller is a two-wire bus that support multiple devices both as Masters and Slaves. Generally, a bus Master device:

- initiates a bus transfer between it and a single SMBus Slave.

- provides the clock signals.

The SMBus 2.0 Controller is based on the *System Management Bus (SMBus) Specification*, Version 2.0 and was introduced as an alternative higher-power set of electrical characteristics versus the earlier version 1.0 and 1.1. This higher-drive capability is required when implementing PCI Express throughout the system. These host controllers are part of the S12x0 System Management Transport and are treated as integrated PCI endpoint devices. It also enabled Plug and Play support.

## 1.2.3 Legacy I/O Features

The Legacy Block consists of legacy modules some of which are required for Windows and other PC OS hardware compatibility.

The Legacy Block consists of modules like Real Time Clock, Timers, Interrupt Controllers, General Purpose I/O, LPC Interface, etc.

- Timers:

- 8254 Programmable interval Timers (PIT).

- Real-Time Clock (RTC).

- High-Precision Event Timer (HPET).

- Interrupt Controller:

- 8259 Programmable Interrupt Controllers (PIC).

- I/O Advanced Programmable Interrupt Controller (IOAPIC) 1.1.

- Interfaces:

- High-Speed UART.

- Low Pin Count (LPC) 1.1.

- General-Purpose I/O (GPIO).

- Serial Peripheral Interface (SPI).

- SMBus 1.0 Controller.

- Miscellaneous:

- Interrupt Routing.

- GPIO Functional MUXing.

## **1.3 Power Management Support**

#### **1.3.1** Power Management Features

Below are the S12x0 power management features:

- ACPI Platform Sleep State support: S0, S3, S4, S5

- ACPI Processor (CPU) C States: C0, C1, C2, C4, C6

- ACPI Device States: D0, D3

- PCI Express: L0, L0s, L1, L2, L3

- Enhanced Intel SpeedStep® Technology

- Hardware throttling

- Clock Gating

- Thermal throttling

- Dynamic I/O power reductions (disabling sense amps on input buffers, tri-stating output buffers)

- Reprogrammable Power Management Unit (PMU)

- Reprogrammable thermal management algorithms performed by PMU

- DDR3 SDRAM memory controller and PHY:

- Dynamic Rank Power Down

- Dynamic power down is employed during normal operation. If all the pages have been closed at the time of CKE pin de-assertion, the SDRAM devices enter the precharge power-down state. Otherwise the devices enter the active power-down state.

- Conditional Memory Self-Refresh

- DLL master/slave shutdown based on CPU state

- Address and command signal tri-state when all memory is in power-down, self-refresh, or when not in use (no chip select asserted)

- Chip-select tri-state for a powered-down row

- Clock tri-stating for unpopulated DIMMs

- CKE/CS tri-stating for unpopulated rows

- Conditional Memory Self-Refresh during C2-C4-C6

- Conditional and software directed Memory Self-Refresh Supports conditional self-refresh entry in the C2-C6 states, based on memory request traffic from host interface agents

- · Debug and Testability hooks

## **1.4 Thermal Management Support**

The S12x0 implements configurable forms of Thermal Management for itself, the DDR3 SDRAM, and system-level thermal limits. It supports both thermal-sensor-based and event-counter-based thermal management. It has several forms of threshold evaluation called trip mechanisms. It also has one configurable form of threshold enforcement called throttling with four unique limits.

The S12x0 contains many techniques to help better manage thermal attributes of the processor:

- Intel<sup>®</sup> Thermal Monitor and Intel<sup>®</sup> Thermal Monitor 2:

- Provides thermal management.

- Enhanced Digital Thermal Sensor (DTS):

- One Digital Thermal Sensor per core of the dual-core S12x0.

- Provides per-thread temperature sensing.

For additional information about implementing the thermal-management features in this document, refer to the Thermal/Mechanical Design Guide (TMDG) document for the S12x0.

## 1.5 Package Summary

The S12x0 is manufactured in a 34mm x 28mm Flip-Chip Ball Grid Array (FCBGA) package and consists of a silicon die mounted face down on an organic substrate populated with 1283 solder balls on the bottom side.

## **1.6** Terminology

A '\_N', '#', '\_B', or 'B' symbol after a signal name refers to an active low signal indicating a signal is in the active state when driven to a low level. When RESETB, for example, is low, a reset has been requested.

#### Table 1-3.Processor Terminology (Sheet 1 of 2)

| Term Description                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DDR3                                                                    | Third generation Double Data Rate SDRAM memory technology that is the successor to DDR2 SDRAM                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMA                                                                     | Direct Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| ECC                                                                     | Error Correction Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Enhanced Intel<br>SpeedStep® Technology                                 | Allows the operating system to reduce power consumption when performance is not needed.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Execute Disable Bit                                                     | The Execute Disable bit allows memory to be marked as executable or non-executable, when combined with a supporting operating system. If code attempts to run in non-executable memory the processor raises an error to the operating system. This feature can prevent some classes of viruses or worms that exploit buffer overrun vulnerabilities and can thus help improve the overall security of the system. See the <i>Intel</i> ® <i>64 and IA-32 Architectures Software Developer's Manuals</i> for more detailed information. |  |

| 110                                                                     | The Integrated I/O Controller. An I/O controller that is integrated in the processor die.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| іМС                                                                     | The Integrated Memory Controller. A Memory Controller that is integrated in the processor die.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Intel <sup>®</sup> 64 Technology                                        | 64-bit memory extensions to the IA-32 architecture. Further details on Intel 64 architecture and programming model can be found at http://developer.intel.com/technology/intel64/.                                                                                                                                                                                                                                                                                                                                                     |  |

| Intel <sup>®</sup> Virtualization<br>Technology (Intel <sup>®</sup> VT) | Processor Virtualization which when used in conjunction with Virtual Machine<br>Monitor software enables multiple, robust independent software environments<br>inside a single platform.                                                                                                                                                                                                                                                                                                                                               |  |

| Integrated Heat Spreader<br>(IHS)                                       | A component of the processor package used to enhance the thermal<br>performance of the package. Component thermal solutions interface with the<br>processor at the IHS surface.                                                                                                                                                                                                                                                                                                                                                        |  |

| Jitter                                                                  | Any timing variation of a transition edge or edges from the defined Unit Interval (UI).                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| LLC                                                                     | Last Level Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| LRU                                                                     | Least Recently Used. A term used in conjunction with cache hierarchy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| MLC                                                                     | Mid Level Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| PCODE                                                                   | Power Management Unit (PMU) micro-code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| PMU                                                                     | Power Management Unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| PCI Express                                                             | PCI Express Generation 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Processor                                                               | The 64-bit, single-core or multi-core component (package)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Processor Core                                                          | The term "processor core" refers to Si die itself which can contain multiple execution cores. Each execution core has an instruction cache, data cache, and 256-KB L2 cache.                                                                                                                                                                                                                                                                                                                                                           |  |

| Rank                                                                    | A unit of DRAM corresponding four to eight devices in parallel, ignoring ECC.<br>These devices are usually, but not always, mounted on a single side of a DDR3<br>DIMM.                                                                                                                                                                                                                                                                                                                                                                |  |

| SSE                                                                     | Intel® Streaming SIMD Extensions (Intel® SSE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| So-DIMM                                                                 | Small outline Dual In-line Memory Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Table 1-3. | <b>Processor Terminology</b> | (Sheet 2 of 2) |

|------------|------------------------------|----------------|

| Table 1-3. | FIUCESSUI TETTITUUUUU        | (SHEEL Z UI Z) |

| Term            | Description                                                                                                                                                                                                                                                                                                                                  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SMBus           | System Management Bus. A two-wire interface through which simple system and power management related devices can communicate with the rest of the system. It is based on the principals of the operation of the I2C* two-wire serial bus from Philips Semiconductor.                                                                         |  |

| TAC             | Thermal Averaging Constant                                                                                                                                                                                                                                                                                                                   |  |

| TDP             | Thermal Design Power                                                                                                                                                                                                                                                                                                                         |  |

| TSOD            | Temperature Sensor On DIMM                                                                                                                                                                                                                                                                                                                   |  |

| UDIMM           | Unbuffered Dual In-line Memory Module                                                                                                                                                                                                                                                                                                        |  |

| Unit Interval   | Signaling convention that is binary and unidirectional. In this binary signaling, one bit is sent for every edge of the forwarded clock, whether it be a rising edge or a falling edge. If a number of edges are collected at instances $t_1$ , $t_2$ , $t_n$ ,, $t_k$ then the UI at instance "n" is defined as:<br>UI $_n = t_n - t_{n-1}$ |  |

| V <sub>CC</sub> | Processor core power supply                                                                                                                                                                                                                                                                                                                  |  |

| V <sub>SS</sub> | Processor ground                                                                                                                                                                                                                                                                                                                             |  |

| x1              | Refers to a Link or Port with one Physical Lane                                                                                                                                                                                                                                                                                              |  |

| x4              | Refers to a Link or Port with four Physical Lanes                                                                                                                                                                                                                                                                                            |  |

| x8              | Refers to a Link or Port with eight Physical Lanes                                                                                                                                                                                                                                                                                           |  |

## **1.7** Related Documents

Refer to the following documents for additional information.

#### Table 1-4.Related Documents

| Document†                                                                                                                                                                                                                                                                                                                                                                                                          | Document<br>Number/Location                                       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|

| Processor Documents                                                                                                                                                                                                                                                                                                                                                                                                |                                                                   |  |  |  |

| Intel® Atom <sup>™</sup> Processor S1200 Product Family for Microserver Datasheet, Volume 2 of 2                                                                                                                                                                                                                                                                                                                   | 328195                                                            |  |  |  |

| Intel® Atom <sup>™</sup> Processor S1200 Product Family for Microserver<br>Thermal/Mechanical Design Guide (TMDG)                                                                                                                                                                                                                                                                                                  | 328196                                                            |  |  |  |

| Intel® Atom <sup>™</sup> Processor S1200 Product Family for Microserver<br>Boundary Scan Description Language (BSDL) File                                                                                                                                                                                                                                                                                          | 328197                                                            |  |  |  |

| Intel® Atom <sup>™</sup> Processor S1200 Product Family for Microserver Specification Update                                                                                                                                                                                                                                                                                                                       | 328198                                                            |  |  |  |

| Public Specifications                                                                                                                                                                                                                                                                                                                                                                                              |                                                                   |  |  |  |

| Advanced Configuration and Power Interface Specification 3.0                                                                                                                                                                                                                                                                                                                                                       | http://www.acpi.info                                              |  |  |  |

| PCI Local Bus Specification, Revision 3.0<br>(February 3, 2004)<br>PCI Local Bus Specification, Revision 2.1<br>(November 18, 2010; plus Errata)                                                                                                                                                                                                                                                                   |                                                                   |  |  |  |

| PCI Express Base Specification, Revision 3.0<br>(November 10, 2010)                                                                                                                                                                                                                                                                                                                                                | http://www.pcisig.com/<br>specifications                          |  |  |  |

| <i>PCI-to-PCI Bridge Architecture Specification</i> , Revision 1.2 (June 9, 2003)                                                                                                                                                                                                                                                                                                                                  |                                                                   |  |  |  |

| PCI Bus Power Management Interface Specification, Revision 1.2 (March 3, 2004)                                                                                                                                                                                                                                                                                                                                     |                                                                   |  |  |  |

| DDR3 SDRAM Specification                                                                                                                                                                                                                                                                                                                                                                                           | http://www.jedec.org                                              |  |  |  |

| <ul> <li>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manuals<br/>Volume 1: Basic Architecture</li> <li>Volume 2A: Instruction Set Reference, A-M</li> <li>Volume 2B: Instruction Set Reference, N-Z</li> <li>Volume 3A: System Programming Guide</li> <li>Volume 3B: System Programming Guide</li> <li>Intel<sup>®</sup> 64 and IA-32 Architectures Optimization Reference Manual</li> </ul> | http://www.intel.com/p<br>roducts/processor/manu<br>als/index.htm |  |  |  |

## 1.8 State of Data

The data contained within this document is the most accurate information available by the publication date of this document.

## 2 Interfaces

## 2.1 Integrated Memory Controller

### 2.1.1 Introduction

The S12x0 contains an integrated 72-bit, single channel Memory Controller (iMC) that supports discrete DDR3 DRAM devices, a single dual-rank DDR3 UDIMM/SO-DIMM, or two single-rank DDR3 UDIMMs/SO-DIMMs.

The data bus width of 72 bits supports 64-bit data and an 8-bit ECC. The memory controller supports data rates from 800MT/s to 1333MT/s. The supported DRAM device densities are 1Gb, 2Gb and 4Gb. The SDRAM device data width is either x8 or x16 and the memory controller supports either 1 or 2 ranks. Note that x16 devices are only supported in non-ECC configurations. Currently, there has been no post-Silicon validation of any ECC enabled x16 device configurations. ECC DIMMs do not use x16 devices.

### 2.1.2 Supported Features

The key features of the DDR3 memory interface are summarized in the following list.

- Single channel DDR3 memory controller:

- One- or two- rank Unbuffered DIMMs (UDIMMs) and Small-Outline DIMMS (SO-DIMMs) supported.

- UDIMM support is for 1.5V devices only.

- SO-DIMM support for both 1.5V and Low Voltage (LV) 1.35V SO-DIMMs.

- DRAM speeds supported: 800, 1067 (*the maximum speed supported for Low-Voltage SO-DIMM*), and 1333 MT/s.

- Supports total memory size of 512MB up to 8GB:

- Supports x8 DRAM device widths (ECC and non-ECC configurations).

- Supports x16 DRAM device width only with non-ECC configurations

- Supports 1Gb, 2Gb and 4Gb DRAM device densities.

- Supports 1 or 2 ranks (2 chip selects), dual ranks must be identical.

- 72-bit data bus (64-bit data and 8-bit SEC-DED-ECC).

- Supported data reliability features:

- Demand and Patrol memory scrub.

- Error injection on write/read data paths including address matching.

- DDR Data Scrambler to reduce power supply noise, improve signal integrity and to encrypt/protect the contents of memory.

- Supports different physical address mappings to optimize for performance.

- Aggressive power management to reduce power consumption.

- Supports 1N/2N/3N mode for DRAM command.

- Out-of-order request service for increased performance.

- Opportunistic and per-rank refresh for reduced performance impact.

## 2.1.3 Functional Description

The DDR3 Memory Controller supports three DDR3 transfer rates:

- 800MT/s (6.4GB/s).

- 1067MT/s (8.5GB/s).

- 1333MT/s (10.7GB/s).

Serial Presence Detect (SPD) discovery is used by BIOS to determine the number of DIMMs populated, the number of ranks per DIMM, the device width, density and the speed.

#### 2.1.3.1 DRAM Requests and Data Ordering

The memory controller supports four unique command requests from the root complex:

- 32 byte write, 32 byte aligned (address [4:0] = 0).

- 64 byte write, 64 byte aligned (address [5:0] = 0).

- 32 byte read, 32 byte aligned (address [4:0] = 0).

- 64 byte read, 32 byte aligned (address [4:0] = 0).

The memory controller does not support partial writes because of the ECC protection and because the DDR3 I/O signals do not support data masks. The root complex is configured to disable partial writes by performing an underfill read, followed later by a full 32 or 64 byte write.

The memory controller can reorder the root complex requests ito optimize the memory bandwidth. It operates, however, under the following restrictions:

- Requests that address the same cache line (address[35:6]) are performed in the same order as received from the root complex

- Requests are performed in order if this feature is disabled (DSCH[8]=1) or if a request has reached the out-of-order aging threshold (DSCH[4:0]).

#### 2.1.3.2 DRAM Out of Bound Access

The iMC sends an out-of-bound write access to DDR3 memory without any chip selects asserted low. This prevents the corruption of the memory. Out-of-bound read accesses are sent to DDR3 memory but the memory controller returns 0xFF data to the internal memory arbitration unit of the S12x0. This is done to prevent data from secured addresses returning by wrapped around addresses.

*Note:* In a correctly configured system, the memory controller should never receive an out of bounds access from the SoC Root Complex.

### 2.1.3.3 DRAM Power Management

Power Management involves managing and reducing the power consumed by both the memory controller and the DRAM devices. The DRAM devices provide two ways to reduce power consumption: Power Down mode and Self Refresh. The memory controller manages these two power saving modes, and in addition, controls a number of its own components to further reduce power consumption. The memory controller supports memory power management in the following conditions:

- Active Power Down No commands are visible for the rank, the rank power down idle timer has expired and one or more pages are open

- **Pre-charge Power Down** No commands are visible for the rank, the rank power down idle timer has expired and all pages are closed

- **Dynamic Self Refresh** Dynamic self-refresh is enabled, all pages in all ranks are closed, no commands in the command queue or being received from the north cluster, the status priority level from the root is below 2, and the self-refresh idle timer has expired

- Self Refresh If enabled, entered when the system transitions to suspend mode.

#### 2.1.3.3.1 Power Down Modes

When DRAM is in Power-Down mode, all input and output buffers are deactivated, excluding CK, CK#, ODT, CKE and RESET#, and the DRAM internal clock is disabled. Power- Down is applied per rank whenever a rank is inactive. DDR3 supports 3 types of Power-Down modes: **Active Power-Down** (*at least one bank in the PD rank is open*), **Precharge Power-Down** (*all banks in the PD rank are closed*) and **DLLoff mode**. The DLLoff mode is only supported as long as the ranks are self terminating. This means that the DODT register is configured to drive only the same rank ODT signal as the rank targeted with the read/write command.

The memory controller supports a programmable power management command that is sent to the DDRIO physical layer to enter a low power mode. The selection of low power mode is entered is based upon power savings versus self-refresh exit latency. In general, the higher power saving states require larger self-refresh exit latencies because it takes longer to power on all of the features.

#### 2.1.3.3.2 Dynamic Self Refresh Mode

The memory controller also supports Dynamic Self Refresh during normal operation to support the maximum power savings mode. It wakes the memory from Self Refresh whenever a memory request is received, then re-enters Self Refresh mode when the memory controller is idle and the self-refresh timer expires.

#### 2.1.3.3.3 Page Management

The memory controller is capable of closing pages after the page has been idle for a configurable period of time. This benefits the system for both power and performance. From a performance standpoint, it helps since it can reduce the number of page misses encountered. From a power perspective, it allows the memory devices to reach the precharge power management state (*power down when all banks are closed*), which has better power saving characteristics on most memory devices than when the pages are left open and the device is in Active Power-Down mode.

#### 2.1.3.3.4 Self Refresh Modes

Self Refresh can be used to retain data in the DRAM devices even if the rest of the system is powered down. When the memory is in Self Refresh, the memory controller disables all output signals except the CKE and RESET# signals. Self-Refresh has 2 main usage modes:

- Power-saving during S0 idle periods.